外延片的制作過程廣東萬硅可以提供超厚外延片及高阻外延片(EPI)

外延層

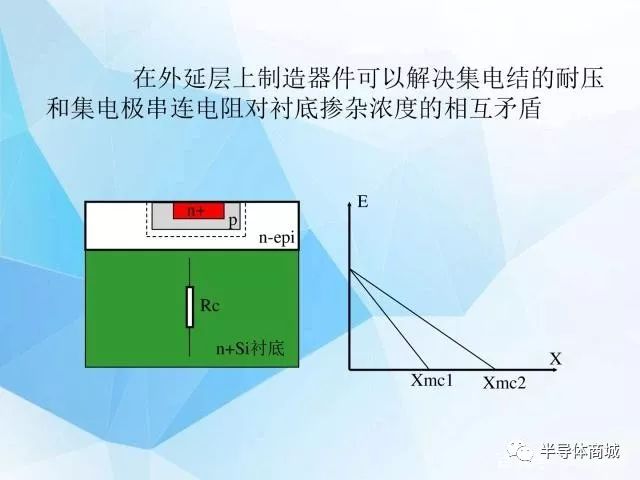

對于集成電路制造商硅峰提供在襯底上具有埋入離子注入或擴散層的硅外延沉積服務。  根據生長方法可以將外延工藝分為兩大類(表1):全外延(Blanket Epi)和選擇性外延(Selective Epi, 簡稱SEG)。工藝氣體中常用三種含硅氣體源:硅烷(SiH4),二氯硅烷(SiH2Cl2, 簡稱DCS) 和三氯硅烷(SiHCl3, 簡稱TCS);某些特殊外延工藝中還要用到含Ge和C的氣體鍺烷(GeH4)和甲基硅烷(SiH3CH3);選擇性外延工藝中還需要用到刻蝕性氣體氯化氫(HCl),反應中的載氣一般選用氫氣(H2)。" ~1 X. i9 V% A7 I 外延選擇性的實現一般通過調節外延沉積和原位(in-situ)刻蝕的相對速率大小來實現,所用氣體一般為含氯(Cl)的硅源氣體DCS,利用反應中Cl原子在硅表面的吸附小于氧化物或者氮化物來實現外延生長的選擇性;由于SiH4不含Cl原子而且活化能低,一般僅應用于低溫全外延工藝;而另外一種常用硅源TCS蒸氣壓低,在常溫下呈液態,需要通過H2鼓泡來導入反應腔,但價格相對便宜,常利用其快速的生長率(可達到5 um/min)來生長比較厚的硅外延層,這在硅外延片生產中得到了廣泛的應用。IV族元素中Ge的晶格常數(5.646A與Si的晶格常數(5.431A差別最小,這使得SiGe與Si工藝易集成。在單晶Si中引入Ge形成的SiGe單晶層可以降低帶隙寬度,增大晶體管的特征截止頻率fT(cut-off frequency),這使得它在無線及光通信高頻器件方面應用十分廣泛;另外在先進的CMOS集成電路工藝中還會利用Ge跟Si的晶格常數失配(4%)引入的晶格應力來提高電子或者空穴的遷移率(mobility),從而增大器件的工作飽和電流以及響應速度,這正成為各國半導體集成電路工藝研究中的熱點。 由于本征硅的導電性能很差,其電阻率一般在200ohm-cm以上,通常在外延生長的同時還需要摻入雜質氣體(dopant)來滿足一定的器件電學性能。雜質氣體可以分為N型和P型兩類:常用N型雜質氣體包括磷烷(PH3)和砷烷(AsH3),而P型則主要是硼烷(B2H6)。 |